Loading

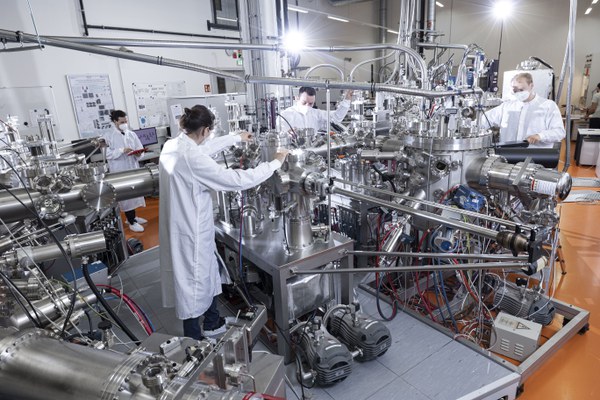

Die Zukunft der Materialien gestalten.

Das Institut erforscht grundlegende Fragen der Halbleiterphysik, der Photonik, der topologischen Materialien sowie Bauelemente für Quantencomputer und neuromorphes Computing.

Institutsleiter: Prof. Dr. Detlev Grützmacher

Veranstaltungen

Halbleiter-Nanoelektronik (PGI-9)

Loading