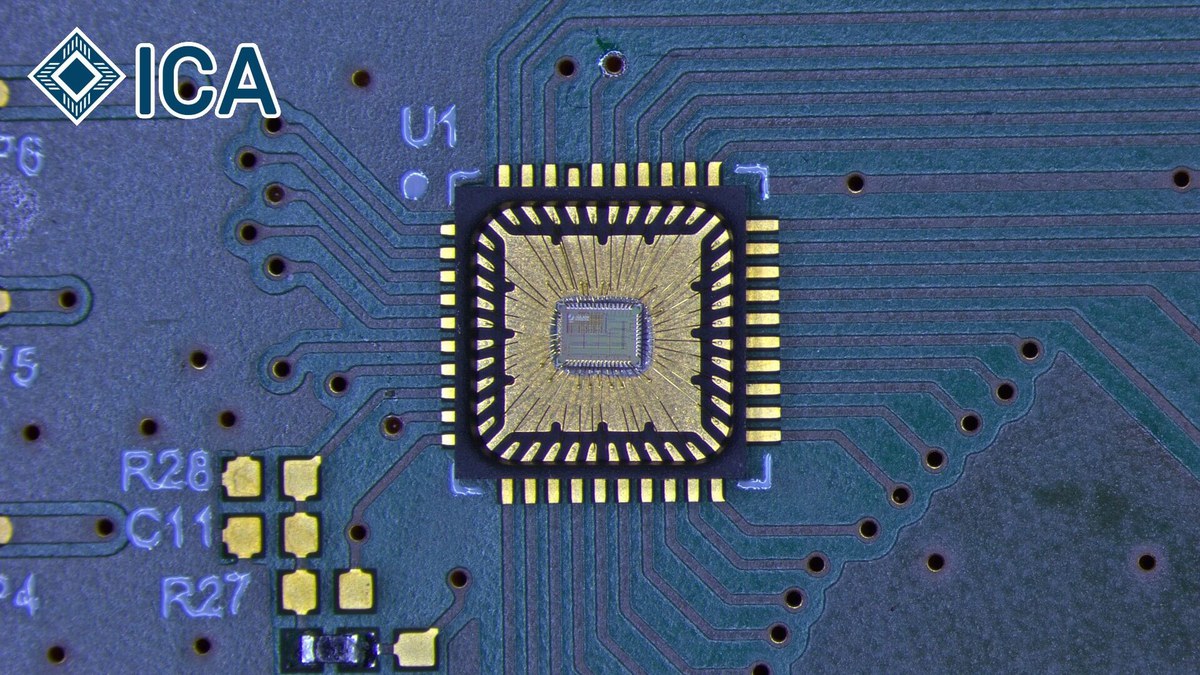

Introducing Dolphin.SNN: A 28 nm Coupled Oscillator Chip for Advanced Network and Computing Research

We are happy to share that coupled oscillator chip Dolpin.SNN, is here!

Dolphin.SNN, implemented in 28 nm process technology, is inspired by the Kuramoto model with delay to emulate real-world systems. This chip serves as a platform for studying coupled oscillators where each oscillator is represented by a Phase Locked Loop (PLL).

It will be used to analyze coupled oscillator dynamics under different coupling schemes by going beyond traditional simulation approaches. Such a platform could pave way for future implementations in analyzing large-scale networks such as power grids or for computing using Oscillatory Neural Network (ONNs).

This work has been supported by the German Federal Ministry of Education and Research (BMBF) with grant number 16ME0398K.

Last Modified: 10.03.2025