Project: NEUROTEC II

Goals

The Demonstrator Project (DP) work package focuses on developing systems, circuits, and technologies to gain in-depth insights into memristor integration, control, and operation, with the goal of creating commercially viable, technology-transferable solutions.

Contacts

Project Description

The BMBF-funded NEUROTEC project is at the forefront of advancing high-tech capabilities and fostering structural transformation in the digitalization sector. It focuses on the development of innovative neuromorphic electronic hardware and accompanying software, with the memristive cell as its core technology, utilizing various physical memory mechanisms. Through a combination of fundamental research and the creation of demonstrators, the project collaborates closely with industry partners in the Rhineland region, driving technological progress and industrial innovation. Together with its sister project NeuroSys thriving economic ecosystem for neuromorphic AI hardware and software in the Aachen-Jülich region is envisaged.

Find out more about NEUROTEC.

This work has been supported by the German Federal Ministry of Education and Research (BMBF) with grant number 16ME0398K.

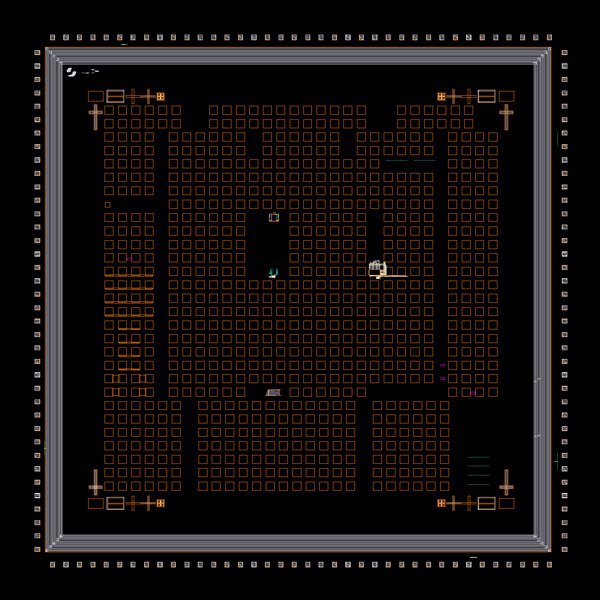

Tapedout Chips under NEUROTEC II

- 6x6 mm 28nm CMOS Chip

- Integrated CMOS structures for 1T1R, 2T1R memristor units

- Integrated Content Addressable Memory units and arrays

- Integrated Compute in Memory unit and arrays

- VCM and PCM mode memristor units

- 1.4 x 1 mm 28nm CMOS Chip in QFN 40

- Integrated Memristor Control circuit HRS, LRS and read for 2 x 2 arrays

- Current mode SAR ADC with adaptive Dynamic range

- Integrated RISC-V and memory for error correction and control

- 1.4 x 1 mm 28nm CMOS Chip in QFN 40

- 7 coupled PLLs for Oscillatory Neural Network

- Analog and multilevel phase coupling

- Scalable ONN with all to all and multi cluster coupling