EPI-SGA1/2: CO-DESIGN DES RHEA-CHIPS - BEITRÄGE UND LESSONS LEARNED DES JSC

EPI SGA2

2018 startete die Europäische Union ein langfristiges Programm mit dem Ziel, einen stromsparenden Prozessor für das High-Performance Computing (HPC) zu entwickeln. Aus strategischer Sicht soll die European Processor Initiative (EPI) Souveränität Europas bei der Entwicklung von Prozessoren für HPC verschaffen. Phase 1 des Programms lief bis Ende 2021 und widmete sich den wichtigsten Architekturdefinitionen, Spezifikationen und der Entwicklung eines ersten Chipdesigns. In Phase 2 ist ein Hauptthema die Optimierung der Architektur, um im Jahr 2025 ein wettbewerbsfähiges Produkt mit maximalem Rechendurchsatz zu liefern.

JSC Beiträge & Lessons Learned

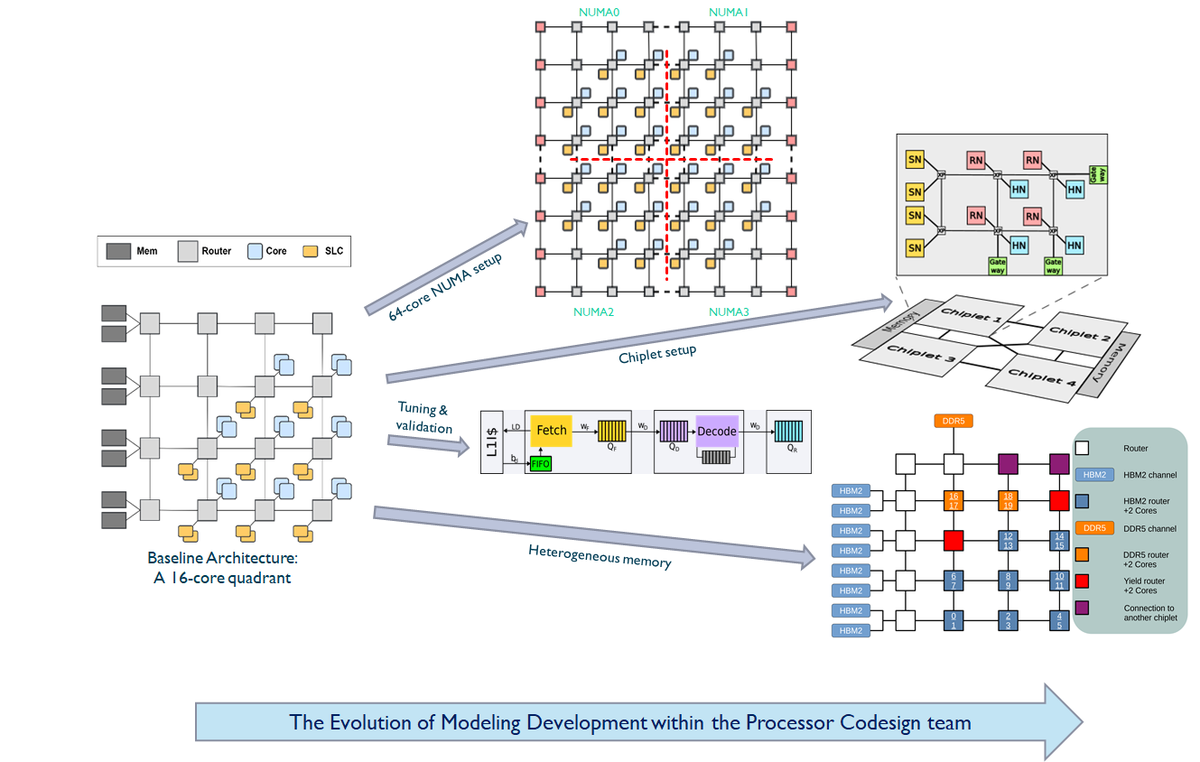

Am JSC leitete das Co-Design-Team der Forschungsgruppe Next Generation Architectures and Prototypes die Codesign- und Validierungsaktivitäten für den EPI-Prozessor der ersten Generation (Rhea1). Darüber hinaus wurde eine Hardware/Software-Codesign-Methode durchgeführt, um optimale Designparameter für die zweite Generation des EPI-Prozessors (Rhea2) und den EPI-Beschleuniger (EPAC v2) zu ermitteln.

Während des Projekts hat das Co-Design-Team erfolgreich die Auswahl von 40 Codes geleitet (veröffentlicht unter https://gitlab.jsc.fz-juelich.de/epi-wp1-public), um SiPEARLs Rhea1-Prozessor für den HPC-Markt zu validieren. Darüber hinaus hat das Team einen gem5-basierten Analyserahmen entwickelt (jetzt öffentlich zugänglich unter https://github.com/FZJ-JSC/gem5-dbc), um die Chips der nächsten Generation mitzuentwickeln.

Zu den wichtigsten Co-Design-Beispielen gehören die Erforschung der Network-on-Chip-Leistung[a], der Leistung des Speichersubsystems[b], der Auswirkungen der NUMA-Architekturkonfiguration[c], einer heterogenen speicherbewussten Prefetching-Technik[d] sowie der Modellierung und Analyse des Chiplet-basierten Designs[f,g]. Die letzten dieser Ergebnisse werden im Juni auf der ISC-Konferenz in Hamburg, einer der wichtigsten internationalen Konferenzen im HPC-Bereich, vorgestellt. Mit diesen und früheren Arbeiten trägt das an EPI beteiligte JSC-Team dazu bei, die Zukunft der in Europa entwickelten Hochleistungsprozessoren und -beschleuniger zu gestalten.

Förderung: The European High Performance Computing Joint Undertaking (JU) under Framework Partnership Agreement No 800928 and Specific Grant Agreement No 101036168 (EPI SGA2).

Mehr Informationen: https://www.european-processor-initiative.eu

Literatur:

[a] L. Zaourar et al., "Multilevel simulation-based co-design of next generation HPC microprocessors". PMBS 2021. DOI: https://doi.org/10.1109/PMBS54543.2021.00008.

[b] A. Portero et al., “COMPESCE: A Co-design Approach for Memory Subsystem Performance Analysis in HPC Many-Cores”. ARCS 2023. DOI: https://link.springer.com/chapter/10.1007/978-3-031-42785-5_8.

[c] L. Zaourar et al., "Case Studies on the Impact and Challenges of Heterogeneous NUMA Architectures for HPC". ARCS 2024. DOI: https://doi.org/10.1007/978-3-031-66146-4_17.

[d] B. Saglam et.al., “Data Prefetching on Processors with Heterogeneous Memory”. MEMSYS 2024. DOI: https://doi.org/10.1145/3695794.3695800.

[f] F. Schätzle, et. al., “Modeling methodology for multi-die chip design based on gem5/SystemC co-simulation”. RAPIDO 2024. DOI: https://doi.org/10.1145/3642921.3642956.

[g] F. Schätzle, et. al., “Modeling Chiplet-to-Chiplet (C2C) Communication for Chiplet-based Co-Design”. ISC 2025 (To appear).