EPI-SGA1/2: CO-DESIGNING THE RHEA CHIP - JSC CONTRIBUTIONS & LESSONS LEARNED

The EPI SGA2

In 2018, the European Union started a long-term program with the goal of developing a low-power High-Performance Computing (HPC) processor. From a strategic point of view, the European Processor Initiative (EPI) shall provide Europe sovereignty in the processor design for HPC. Phase 1 of the program ran until the end of 2021 and was devoted to major architecture definitions, specifications, and the development of a first chip design. In Phase 2, one major topic is architecture optimization in order to deliver a competitive product with maximum compute throughput in 2025.

JSC Contributions & Lessons learned

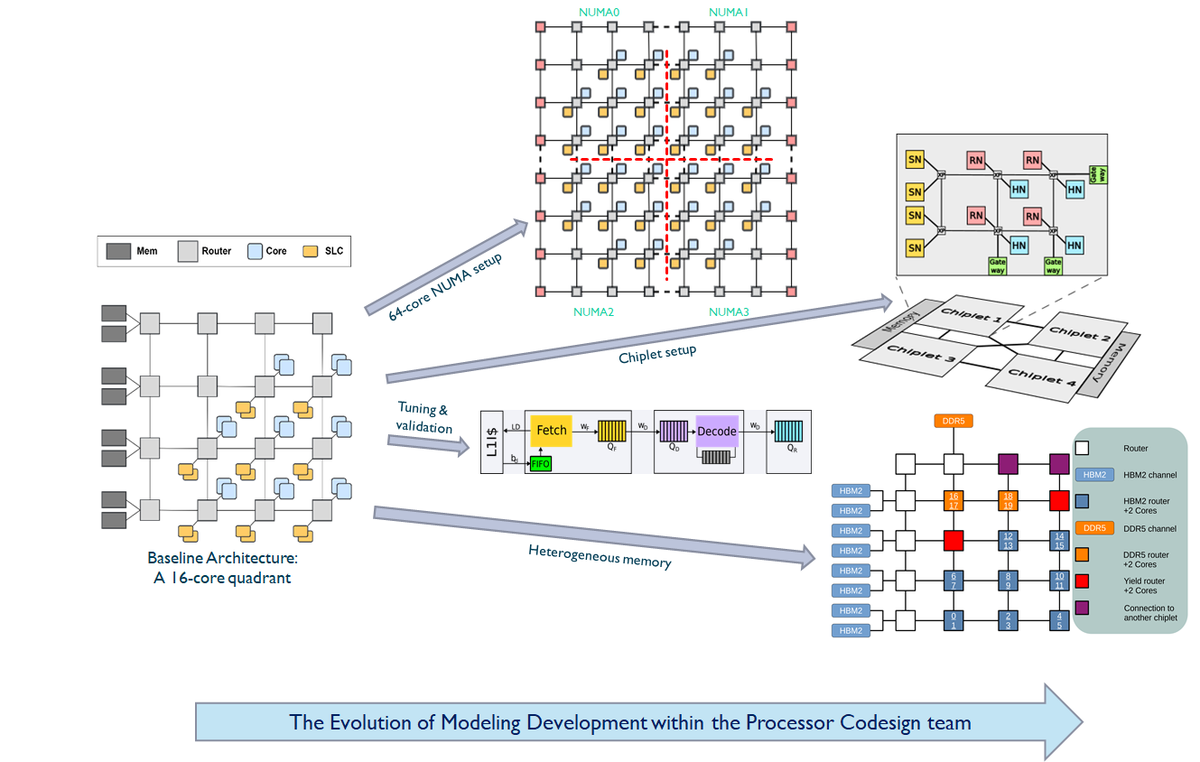

At JSC, the co-design team in the Research Group Next Generation Architectures and Prototypes led the codesign and validation activities for the EPI’s first generation processor (Rhea1). Furthermore, a hardware/software co-design methodology was performed to identify optimal design parameters for the second generation of EPI processor (Rhea2) and EPI accelerator (EPAC v2).

During the project, the co-design team has successfully led the selection of 40 codes (released at https://gitlab.jsc.fz-juelich.de/epi-wp1-public) to validate SiPEARL’s Rhea1 processor for the HPC market. In addition, the team has developed a gem5-based analysis framework (now publicly available at https://github.com/FZJ-JSC/gem5-dbc) to co-design the next-generation chips. Key co-design examples include the exploration of Network-on-Chip performance[a], memory subsystem performance[b],the impact of NUMA architecture configuration[c], a heterogeneous Memory-aware prefetching technique[d], modeling & analysis of chiplet-based design[f,g]. The last of these results will be presented in June at the ISC conference in Hamburg, one of the most important international conferences in HPC. With this and previous work, the JSC team participating in EPI is contributing to shape the future of high-performance processors and accelerators developed in Europe.

Funding: The European High Performance Computing Joint Undertaking (JU) under Framework Partnership Agreement No 800928 and Specific Grant Agreement No 101036168 (EPI SGA2).

More information: https://www.european-processor-initiative.eu

References:

[a] L. Zaourar et al., "Multilevel simulation-based co-design of next generation HPC microprocessors". PMBS 2021. DOI: https://doi.org/10.1109/PMBS54543.2021.00008.

[b] A. Portero et al., “COMPESCE: A Co-design Approach for Memory Subsystem Performance Analysis in HPC Many-Cores”. ARCS 2023. DOI: https://link.springer.com/chapter/10.1007/978-3-031-42785-5_8.

[c] L. Zaourar et al., "Case Studies on the Impact and Challenges of Heterogeneous NUMA Architectures for HPC". ARCS 2024. DOI: https://doi.org/10.1007/978-3-031-66146-4_17.

[d] B. Saglam et.al., “Data Prefetching on Processors with Heterogeneous Memory”. MEMSYS 2024. DOI: https://doi.org/10.1145/3695794.3695800.

[f] F. Schätzle, et. al., “Modeling methodology for multi-die chip design based on gem5/SystemC co-simulation”. RAPIDO 2024. DOI: https://doi.org/10.1145/3642921.3642956.

[g] F. Schätzle, et. al., “Modeling Chiplet-to-Chiplet (C2C) Communication for Chiplet-based Co-Design”. ISC 2025 (To appear).