Prozessor Co-Design

Die Leistung, die ein Anwendungscode auf einem Computer erzielt, hängt vollständig von den Architekturmerkmalen und dem Design des verwendeten Prozessors ab.

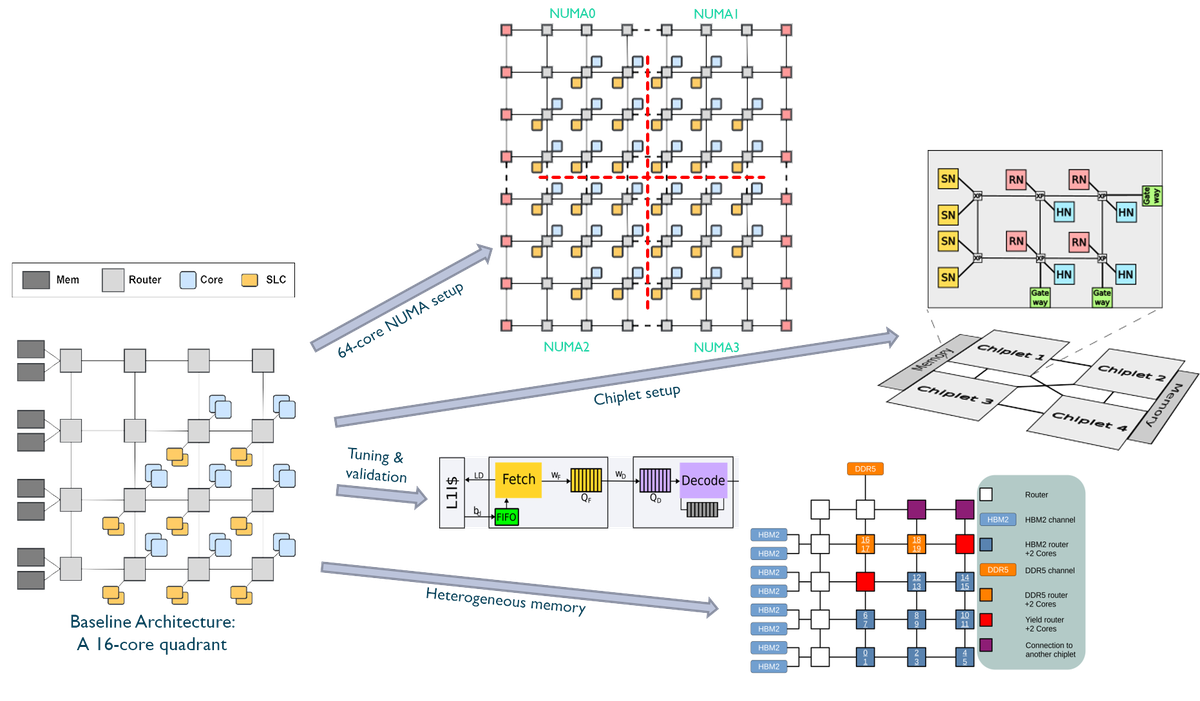

Das Prozessor-Codesign-Team innerhalb der Forschungsgruppe „Next Generation Architectures and Prototypes“ analysiert verschiedenen Chip-Design-Parametern und deren Auswirkungen auf die Anwendungsleistung. Wir bilden die gesamte Komplexität des Chips in unserem gem5-Simulator ab (z. B. Anzahl der Kerne, Speicher- und Cache-Hierarchie, genaue Network-on-Chip-Eigenschaften, Prefetching-Konfigurationen, Chiplet-Implementierung, Modellkalibrierung usw.) und variieren die gewünschten Parameter. Anschließend führen wir Benchmarks durch, die repräsentativ für HPC-Anwendungslasten sind, und bewerten, welche Konfigurationen die beste Leistung liefern.

Wir haben ein deklaratives Open-Source-Benchmark-Konfigurations-Framework, gem5-DBC, entwickelt, um die Konfiguration komplexer gem5-Setups zu automatisieren, Benchmarks auf reproduzierbare Weise auszuführen und die Ergebnisse zu visualisieren, um die gewünschten Erkenntnisse zu gewinnen.

Unser derzeitiger Schwerpunkt liegt auf fortschrittlichen ARM-basierten Hochleistungs-CPUs. Wir sind Teil der European Processor Initiative (EPI), wo wir die Projektaktivitäten im Bereich „Codesign und Validierung“ leiten. Durch unsere Zusammenarbeit mit dem PGI-4 Institut vom FZJ, und die starken Partnerschaften mit Arm und SiPEARL haben wir Zugang zu den neuesten Informationen über Prozessorarchitekturen und können durch die Erkenntnisse, die wir unseren Partnern durch unsere Arbeit vermitteln, Einfluss auf die nächste Prozessorgeneration nehmen.

Interesse an unsere Arbeit? Schreib gerne Nam an:

Team Leader

Liste unserer jüngsten Veröffentlichungen:

- Schätzle, F. Falquez, C.; Ho, N.; Zambanini, A ; Boom, J. ; Suarez, E. Modeling Chiplet-to-Chiplet (C2C) Communication for Chiplet-based Co-Design. ISC 2025. Open Access (2025)

- Ho, N.; Falquez, C.; Portero, A.; Suarez, E.; Pleiter, D., Memory Prefetching Evaluation of Scientific Applications on A Modern HPC Arm-based Processor, in IEEE Access, (2025), DOI: 10.1109/ACCESS.2025.3569533

- Falquez, C.; Portero, A.; Ho, N.; Schätzle, F.; Suarez, E.; Pleiter, D, gem5-DBC, Software Repository (2024) https://github.com/FZJ-JSC/gem5-dbc

- Saglam, B.; Ho, N; Falquez, C. ; Portero, A.; Schätzle, F.; Suarez, E.; Pleiter, D., Data Prefetching on Processors with Heterogeneous Memory, 10th International Symposium on Memory Systems (MEMSYS24) (2024), DOI:10.1145/3695794.3695800

- Saglam, B., Heterogeneous Memory Aware Prefetching on High Performance Arm Processors, Master Thesis, Rheinische Friedrich-Wilhelms-Universität Bonn, 142 pp. (2024) DOI:10.34734/FZJ-2024-04892

- Zaourar, L.; Benazouz, M.; Mouhagir, A.; Falquez, C.; Portero, A.; Ho, N.; Suarez, E.; Petrakis, P.; Marazakis, M.; Sgherzi, F.; Fernandez, I.; Dolbeau, R.; Pleiter, D., Case Studies on the Impact and Challenges of Heterogeneous NUMA Architectures for HPC, Architecture of Computing Systems: 37th International Conference, ARCS 2024, Potsdam, Germany, May 14–16, 2024, Proceedings, pp 251 - 265, (2024) DOI: 10.1007/978-3-031-66146-4_17

- Schätzle, F.; Falquez, C.; Heinen, S.; Ho, N.; Portero, A.; Suarez, E., Van Den Boom, J.; and Van Waasen, S. 2024. Modeling methodology for multi-die chip design based on gem5/SystemC co-simulation. In Proceedings of the 16th Workshop on Rapid Simulation and Performance Evaluation for Design (RAPIDO '24). Association for Computing Machinery, New York, NY, USA, 35–41. (2024) DOI: 10.1145/3642921.3642956

- Portero, A.; Falquez, C.; Ho, N.; Petrakis, P.; Nassyr, S.; Marazakis, M.; Dolbeau, R.; Cifuentes, J. A. N.; Alvarez, L. B.; Pleiter, D. and Suarez, E. COMPESCE: A Co-design Approach for Memory Subsystem Performance Analysis in HPC Many-Cores. In: Goumas, G., Tomforde, S., Brehm, J., Wildermann, S., Pionteck, T. (eds) Architecture of Computing Systems. ARCS 2023. Lecture Notes in Computer Science, vol 13949. Springer, Cham. (2023) DOI: 10.1007/978-3-031-42785-5_