Processor Co-Design

The performance an application code achieves on a computer depends fully on the architecture characteristics and design of the processor employed.

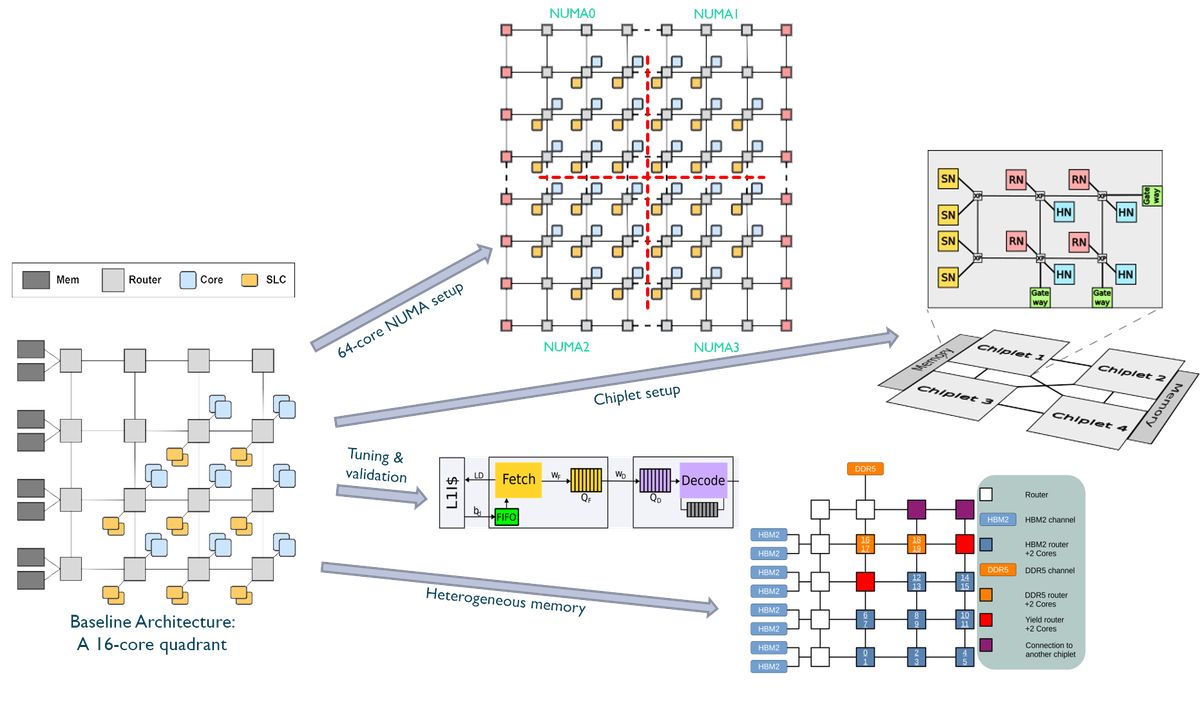

The processor codesign team within the Next Generation Architectures and Prototypes research group analyses trade-offs between different chip design parameters and their impact on application performance. We represent the full complexity of the chip in our gem5 simulator (e.g. number of cores, memory and cache hierarchy, precise network-on-chip characteristics, prefetching configurations, chiplet implementation, model calibration, etc.) and vary the desired parameters. We then run benchmarks that are representative of HPC application workloads and evaluate which configurations deliver the best performance.

We have developed and open-source declarative benchmark configuration framework, gem5-DBC, to automate the configuration of complex gem5 setups, run benchmarks in a reproducible manner, and visualise the results to easily extract the desired insights.

Our current focus is on advanced ARM-based high-performance CPUs. We are part of the European Processor Initiative (EPI), where we lead the project activities in the area of "Codesign and Validation". Our collaboration with FZJ's PGI-4 institute, and strong partnerships with Arm and SiPEARL give us access to the latest processor architecture information, and allow us to influence the next generation processors through the insights we provide to our partners through our work.

Interested in our work? Contact Nam:

Team Leader

Our most recent publications:

- Falquez, C; Long, S.; Ho, N.; Suarez, E.; Pleiter, D. Processor simulation as a tool for performance engineering. Frontiers in High Performance Computing, vol. 3, (2025) DOI=10.3389/fhpcp.2025.1669101

- Schätzle, F. Falquez, C.; Ho, N.; Zambanini, A ; Boom, J. ; Suarez, E. Modeling Chiplet-to-Chiplet (C2C) Communication for Chiplet-based Co-Design. ISC 2025. Open Access (2025)

- Ho, N.; Falquez, C.; Portero, A.; Suarez, E.; Pleiter, D., Memory Prefetching Evaluation of Scientific Applications on A Modern HPC Arm-based Processor, in IEEE Access, (2025), DOI: 10.1109/ACCESS.2025.3569533

- Falquez, C.; Portero, A.; Ho, N.; Schätzle, F.; Suarez, E.; Pleiter, D, gem5-DBC, Software Repository (2024) https://github.com/FZJ-JSC/gem5-dbc

- Saglam, B.; Ho, N; Falquez, C.; Portero, A.; Schätzle, F.; Suarez, E.; Pleiter, D., Data Prefetching on Processors with Heterogeneous Memory, 10th International Symposium on Memory Systems (MEMSYS24) (2024), DOI:10.1145/3695794.3695800

- Saglam, B., Heterogeneous Memory Aware Prefetching on High Performance Arm Processors, Master Thesis, Rheinische Friedrich-Wilhelms-Universität Bonn, 142 pp. (2024) DOI:10.34734/FZJ-2024-04892

- Zaourar, L.; Benazouz, M.; Mouhagir, A.; Falquez, C.; Portero, A.; Ho, N.; Suarez, E.; Petrakis, P.; Marazakis, M.; Sgherzi, F.; Fernandez, I.; Dolbeau, R.; Pleiter, D., Case Studies on the Impact and Challenges of Heterogeneous NUMA Architectures for HPC, Architecture of Computing Systems: 37th International Conference, ARCS 2024, Potsdam, Germany, May 14–16, 2024, Proceedings, pp 251 - 265, (2024) DOI: 10.1007/978-3-031-66146-4_17

- Schätzle, F.; Falquez, C.; Heinen, S.; Ho, N.; Portero, A.; Suarez, E., Van Den Boom, J.; and Van Waasen, S. 2024. Modeling methodology for multi-die chip design based on gem5/SystemC co-simulation. In Proceedings of the 16th Workshop on Rapid Simulation and Performance Evaluation for Design (RAPIDO '24). Association for Computing Machinery, New York, NY, USA, 35–41. (2024) DOI: 10.1145/3642921.3642956

- Portero, A.; Falquez, C.; Ho, N.; Petrakis, P.; Nassyr, S.; Marazakis, M.; Dolbeau, R.; Cifuentes, J. A. N.; Alvarez, L. B.; Pleiter, D. and Suarez, E. COMPESCE: A Co-design Approach for Memory Subsystem Performance Analysis in HPC Many-Cores. In: Goumas, G., Tomforde, S., Brehm, J., Wildermann, S., Pionteck, T. (eds) Architecture of Computing Systems. ARCS 2023. Lecture Notes in Computer Science, vol 13949. Springer, Cham. (2023) DOI: 10.1007/978-3-031-42785-5_8